# 高壓元件的動態性安全操作範圍

# 許健、楊紹明 亞洲大學資訊工程學系

### 一、前言

自 1980 年代,橫向擴散金屬氧化物半導體(LDMOS)由於其高功率、高壓、高能量及高頻而為功率半導體積體電路廣泛地採用[1-3]。隨著元件尺寸的縮小,先進的功率晶片整合技術上,在 LDMOS 電晶體也大幅減少尺寸以利微縮晶片之面積,然而,在小面積元件上會增加熱阻抗,降低 LDMOS 可以承受的最大能量(Energy Capability)在沒有達到過高的溫度時就隨之破壞。也因為這個原因的限制,所以引入了對於安全操作區(safe operating area)即靜態操作區(static SOA)與該元件的能量傳輸能力(energy handling capability)的新挑戰。由於 LDMOS 的可靠性高,因此對於可靠性有重大影響的熱效應一直受到研究重視。在不同溫度環境下,LDMOS元件在熱與電的限制量測下,使用單一脈衝(single pulse safe operating area)的測試,稱之為動態安全操作範圍(Dynamic SOA)或是能量能力(energy capability)。而功率元件的單脈衝雪崩能量(Single Pulse Avalanche Energy)測試是元件規格之一,其失效原因即因自發加熱(Self-heating)產生的高電流及高熱散而造成的[4-7]。因此在元件的動態安全操作範圍的改善就必需要充分了解其元件失效的物理原因,方能預估該元件設計的能量極限及元件設計改善。 所以一個LDMOS 的操作工作條件與單脈衝之脈衝寬度(Pulse width)是決定此一元件可以在不發生熱失控(Thermal-Runaway)的安全操作範圍工作。

本文的目的是討論一個 LDMOS 元件在不同操作溫度環境下的能量極限範圍(Dynamic SOA) 並找出其關係曲線。將利用模擬 800 伏特超高壓 LDMOS 元件與 70 伏特的高壓 LDMOS 元件經過電性測試即單脈衝雪崩能量(Single Pulse Avalanche Energy)測試模擬,與解析方程式預估元件之能量負載計算做比較,對於不同環境失效之原因探討找出其失效的物理原因。本文採取模擬 LDMOS 觀測期元件溫度分布與臨界溫度(Critical Temperature)來分析失效點及物理原因。因此模擬結果與解析方程式預估元件能量負載計算結果非常吻合可以準確預估一個LDMOS 之能量操作極限[10-12]。

#### 二、元件結構說明及測試方法

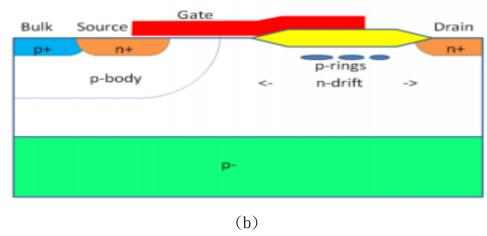

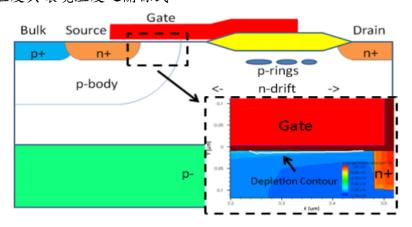

在 2002 年 V. Khenmka et.al.的論文中探討 Single RESURF LDMOS 與 Double RESURF LDMOS 元件的能量能力與環境溫度之關係。該論文宣稱測量出的 Double RESURF LDMOS 的能量極限與環境溫度是呈線性曲線 (Linear Relationship)。而這線性關係也為 H. Hagino et.al. 在 1996 年的 IGBT 元件研究論文提出過 [8-10]。因此,功率元件皆利用外插方法即得到在零能量時的環境溫度,也就是所謂的臨界溫度(Critical Temperature)。V. Khenka et. al 也在同論文中提出 Double RESURF LDMOS 元件的靜態安全操作範圍(Static SOA)遠較 Single RESURF LDMOS 元件佳。因此本文章探討模擬研究也是採用 Double RESURF LDMOS 元件為研究之目標,其測試熱特性(thermal characteristic)與熱安全操作區(Thermal Safe Operating Area; T-SOA),如圖 1 所示 70 伏特 Double RESURF LDMOS 元件模擬剖面結構示意圖,其導通電阻(Ron)及擊穿電壓 (Breakdown)以獲取最大優化(即漂移區已完全空乏,達到電荷平衡)。該元件是利用 Ptop 結構

形成多 RESURF 元件結構,在元件製程與電特性模擬是採用 Synopsys 公司 Sentaurus 元件模擬 軟體。

圖 1:70 伏特 Double RESURF LDMOS 元件之模擬剖面結構示意圖。

#### 三、結果與討論

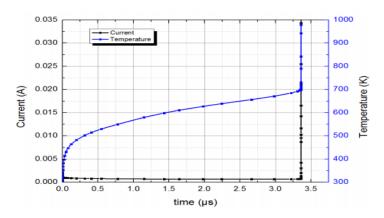

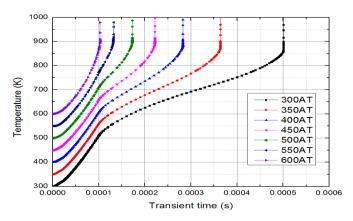

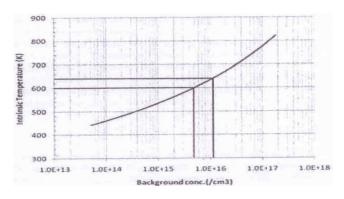

本文所用進行之測試方法乃根據作者在 2011 年所發表 800 伏特的熱安全操作區論文。從 70 伏特元件的源極與汲極端加一脈衝(Pulse width time)電壓(Vds),使元件有一定汲極電流(Ids) 負載直到元件失效,汲極電流會暴衝使元件到達熱失效(Thermal Runaway)狀態,此時可以記 錄脈衝電壓時間,就可藉由汲極電壓、汲極電流與脈衝時間計算獲得元件裝置的能量能力 (Energy Capability)。我們設定元件模擬物理參數 Thermal dynamic mode 的模擬測試,將元件 設定在不同環境的熱電偶合模擬產生的溫度變化進行研究及分析。圖2所示,為 70 伏特 Double RESURF LDMOS 元件,在環境溫度 300K 下,其模擬元件之汲極電流、脈衝時間與臨界 溫度之實驗結果圖。從圖 2 可以觀察到當脈衝時間到達 3.35 微秒, 汲極電流立即飛越高點而 導致元件因熱失控而失效,由於本元件面積尺寸較前述元件小,因此失效的脈衝時間較短。 元件之所以失效是因為元件之自我加熱導效應導致元件內部溫度到達臨界溫度 (critical temperature, Tc)。 臨界溫度的定義是當矽晶體在其該本徵濃度時,其淨有效本徵載子濃度(Nie) 與該晶體之有效參雜濃度相同時。圖3所示為元件在不同的環境溫度下脈衝時間的電 - 熱模 擬。其主要改變設定不同的環境溫度,然後在元件的源極與汲極端加一脈衝(Pulse width time) 電壓(Vds),使元件有一定汲極電流(Ids)負載直到元件失效,汲極電流會暴衝使元件到達熱失 效(Thermal Runaway)狀態,此時可以記錄脈衝電壓時間,就可藉由汲極電壓、汲極電流與脈 衝時間計算獲得元件裝置的能量能力(Energy Capability)。圖4所示為矽晶體材料其摻雜濃度與 本徵溫度之關係圖。

圖 2:70 伏特 Double RESURF LDMOS 元件,在環境溫度 300K下,其模擬元件之汲極電流、脈衝時間與臨界溫度之關係圖。

圖3:元件在不同的環境溫度下脈衝時間的電 - 熱模擬。

圖4:矽晶體材料其摻雜濃度與本徵溫度之關係圖。

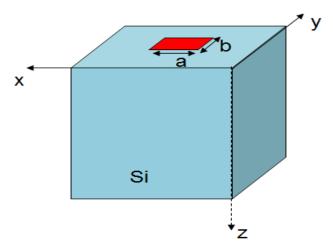

圖 5: 在熱流區域的三維示意圖中,在 z=0 的 a x b 的砂表面的被假定為代表的熱源。

在功率元件計算電和熱的安全工作區其一個分析熱流模型是必要的,所以我們遵循 Dwyer et al.的格林函數方法。在熱流區域的三維示意圖中,如圖 5 在 z=0 的 a x b 的矽表面的被假定為代表的熱源。當一個半導體材料受到矩形面積功率脈衝影響產生熱失效時假設達到臨界溫度,其中,發生過剩的載流子的產生是由於熱效應超過了大多數載流子濃度。對於橫向尺寸的表面熱源 a x b 在半無限介質所示,所以電源故障取決於時間刻度相對於所述特徵擴散時間,關聯於這些尺寸,其中這些時間是指時間 t b 所需的熱梯度分別達到平衡在尺寸 a 和 b 面積下為:

$$t_a = \frac{a^2}{4\pi D} \qquad \text{and} \qquad t_b = \frac{b^2}{4\pi D} \tag{1}$$

能量能力的計算可以由下列的解析方程式及模擬之數據預估。從模擬數據中,能量可由 汲極電壓和電流的乘積與脈衝時間積分得之。另外,也可以利用能量之解析方程式來獲得。 在前述的論文中已有詳述,該解析方程式是利用格林函數得到: [9]

$$E = P_0 X t = \frac{(T_c - T_0)ab\sqrt{\pi K\rho C_p}t}{\int_0^t \tau^{-\frac{1}{2}} \cdot \operatorname{erf}\left(\frac{a}{4\sqrt{D\tau}}\right) \cdot \operatorname{erf}\left(\frac{b}{4\sqrt{D\tau}}\right) \cdot d\tau}$$

(2)

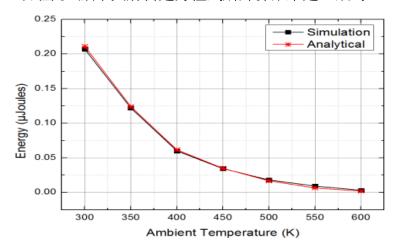

由能量之解析方程式(2)中, $P_0$  是單脈衝功率值(Joule), $T_0$  是臨界溫度(K), $T_0$  是環境溫度(K), $T_0$  a、b 則代表發熱源的 x、y 軸長短 (cm), $T_0$  是質量密度(g/cm3), $T_0$  為矽材料的比熱係數(J/g K),K 是傳導熱係數 (W/cmK),而 D 是熱力擴散係數 (thermal diffusivity,cm²/s),由 K/ $T_0$  以 当值。因此材料的熱導、熱散的溫度效應,在高溫環境下,線性熱膨脹係數也都會考慮在內。我們也觀察到最後結果,在高溫環境測試下,是一非線性曲線與我們模擬的結果是一致的。其元件模擬的結果,如圖  $T_0$  顯示與解析是方程式所計算結果是一致的。

圖 6:元件的能量能力(Energy Capability)與設定環境溫度之模擬結果與解析關係。

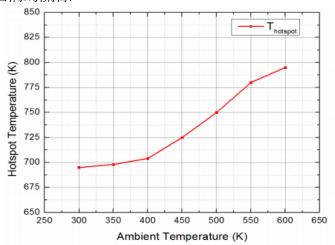

為了探討其功率元件熱失效之物理原因,我們在環境溫度 300K 至 600K 區間進行了更多模擬測試實驗,每隔 50K 進行一次模擬實驗。從實驗中,我們在不同環境溫度模擬實驗下可以得到最高溫度(Maximum temperature) or 熱點 (Hot spot)與脈衝寬時間的關係函數,我們可以觀察到隨環境溫度的故障時間的減少,也增加了近失敗的熱點溫度,如圖 6 所示。所以,元件熱失效的脈衝寬與環境溫度的增加是降低,而這些熱點就是之前所稱的元件臨界溫度。

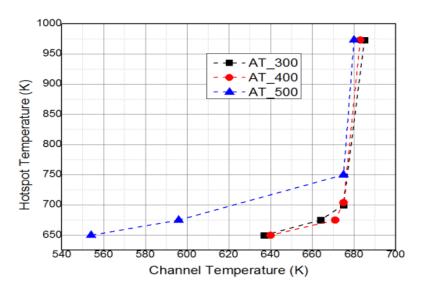

從圖7 也可看出元件熱點在近失效時,也就是臨界溫度隨著環境溫度升高而增高與圖3 所示之曲線相同。在圖8 也顯示出熱點是發生在元件之通道區。當元件溫度高於常溫(300K)時,元件之物理參數會隨著溫度變化而改變元件之熱傳導係數是其中之一。由於熱傳導係數會隨溫度的增高而降低,因此元件的自我加熱(Self-heating)會使元件加速增溫,乃是我們研究失效的機制與元件結構的關係。

圖7:元件熱點溫度與環境溫度之關係式。

圖8:元件溝道空乏區是失效源。

#### 四、失效分析

Khemka et al. (2002) 在 RESURF LDMOS 元件及 H. Hagino et al. (1996) 的 IGBT 元件失效 分析中都提出是因為元件結構中的寄生(Parasitic)雙載子的基-射接面(Base to Emitter junction) 的內建電位(Built-in potential),由於本徵載子濃度因溫度增高而升高。可以使參雜濃度與之相當而終可導致內建電位趨零。也造成基一射接面完全消失,因而元件無法運作而失效,此時的元件最高溫度定義為臨界溫度。

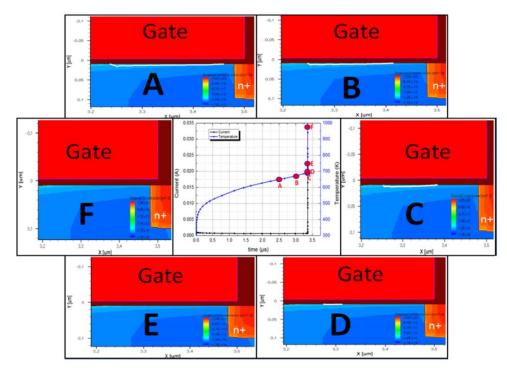

當在元件承受偏壓下,啓動後的元件,通道區會形成空乏區。元件趨近失效時,空乏區開始收縮直至消失,元件到達失效點。圖 9 中顯示是由模擬得出的結果,該結果突顯示了元件在失效前後空乏區的變化。圖 9 中 A 、 B 兩圖是失效前,元件溫度上升,汲極區電流保持不變,空乏區完整無缺。當元件趨近失效點時,圖 9 中的 C、 D 兩圖顯示空乏區逐漸縮小。在圖 9 中的 E、 F 兩圖則是失效後,空乏區已完全消失。此時,模擬已測出元件之本徵載子濃度已相同於其摻雜濃度,也說明了元件達到臨界溫度。

LDMOS 元件失效也可能發生在漂移區(Drift region),因其為高電阻區,當受到偏壓時其產生之焦耳熱能也足以使元件到達臨界溫度。我們也觀察到在漂移區的熱點。圖8 顯示在

通道區有觀察到帶狀的空乏區及熱點。在不同的環境溫度下,我們觀察到同樣的現象。在漂移區及通道區都有熱點產生,熱點的溫度會因環境溫度增高而增加。但是,通道區的熱點溫度則在每一失效時,其溫度不隨環境溫度之變高而有所不同。這是因為在該溫度時,即臨界溫度其元件之本徵濃度與摻雜濃度相同之故。因此元件失效。本實驗之元件其臨界溫度是約680 K。圖10 為熱點溫度與溝道區溫度之對應曲線,從圖中顯示當元件溝道區到達臨界溫度時,元件之漂移區熱點溫度是一致的。

圖9:通道區空乏區與失效前後之變化比較圖。

圖 1 (): 熱點溫度與溝道區溫度之關係。

#### 五、結論

LDMOS 元件在不同環境溫度下,因熱導致失效的物理現象,由模擬及解析計算獲得了一致的結果。元件失效的原因是通道區的溫度因熱而達到臨界溫度。在該溫度下,元件的本 徵載子濃度與摻雜濃度相當,以致於通道區的空乏區消失,導致元件失控而失效。本研究也 發現元件的能量極限與環境溫度是非線性關係 與過去研究發表之線性關係不同。該非線性關係也由模擬及解析計算獲得同樣結論,此關係曲線是預測元件臨界溫度的重要曲線。

## 参考文獻

- [1] P. L. Hower and S. Pendharkar, "Short and long-term safe operating area considerations in LDMOS transistors," in 43'rd Annual International Reliability Physics Symposium, San Jose, pp.545-550, 2005.

- [2] M. A. Belaid, K. Ketata, H. Maanane, M. Gares, K. Mourgues, J. Marcon, "Analysis and simulation of self-heating effects on RF LDMOS devices," in SISPAD-2005, pp.231-234.

- [3] V. Khemka, V. Parthasarathy, R. Zhu, A. Bose and T. Roggenbauer, "Experimental and theoretical analysis of energy capability of RESURF LDMOSFETs and its correlation with static electrical safe operating area (SOA)," in IEEE Transactions on Electron Devices, Vol. 49, No. 6, June 2002.

- [4] D. Dibra, M. Stecher, S. Decker, A. Lindemann, J. Lutz, and C. Kadow, "On the origin of thermal runaway in a trench power MOSFET," in IEEE Trans. Electron Devices, vol. 58, No.10, pp. 3477-3484, Oct.2011.

- [5] P. Hower, J. Lin, S. Haynie, S. Paiva, R. Shaw, and N. Hepfinger, "Safe operating area considerations in LDMOS transistors," in Proc. ISPSD, 1999, pp. 55–58.

- [6] P. L. Hower, J. Lin, and S. Merchant, "Snapback and safe operating area of LDMOS transistors," in IEDM Tech. Dig., 1999, pp. 193–196.

- [7] P. L. Hower, "Safe operating area—A new frontier in LDMOS design," in Proc. Int. Symp. Power Semicond. Devices ICs, 2002, pp. 1–8.

- [8] V. M. Dwyer, A.J. Franklin and D.S. Campbell, "Thermal failure in semiconductor devices," in Solid State Electronics, Vol.33, No.5, pp.553-560, 1990

- [9] Adarsh Basavalingappa, Anumeha, Gene Sheu, "Energy capability of LDMOS as a function of ambient temperature" IEEE 13th International Conference on Ultimate Integration on Silicon (ULIS), Grenoble, France, 2012, in press.

- [10] H. Hagino, J. Yamashita, A. Uenishi, and H. Haruguchi, "An experimental and numerical study on the forward biased SOA of IGBTs," in IEEE Trans. Electron Devices, vol. 43, pp. 490-500, March 1996.

- [11] G. Van den bosch, D. Wojciechowski, B. Elattari, P. Moens and G. Groeseneken, "Characterization of dynamic SOA of power MOSFETs limited by electrothermal breakdown," in Proceedings of ESSDERC, Grenoble, France, 2005.

- [12] S. Merchant, R. Baird, P. Bennett, P. Percy, P. Dupuy and P. Rossel, "Energy capability of lateral and vertical DMOS transistors in an advanced automotive smart power technology," in Proceedings of 1998 ISPSD, Kyoto.

- [13] Sentaurus User's Manual, Version F-2011.09, Synopsys, 2011.

- [14] Glassbrenner, C. J. and G. A. Slack, "Thermal conductivity of silicon and germanium from 3°K to the melting point," in Phys. Rev. 134, 4A (1964) A1058-A1069.

- [15] Shanks, H. R., P. D. Maycock, P. H. Sidles, and G. C. Danielson, "Thermal conductivity of silicon from 300 to 1400°K," in Phys. Rev. 130, 5 (1963) 1743-1748.