# 功率金氧半電晶體 (Power MOSFET) 之簡介

簡鳳佐 逢甲大學電子系

#### 一、前言

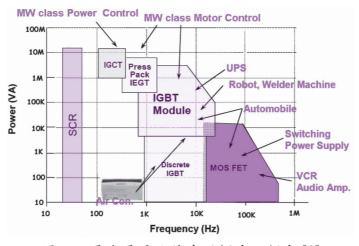

隨著電力需求的增加及節能意識 抬頭,與電力使用效率相關的電力電 子技術,越來越受重視。在日常生活 及各行各業使用的家電及不同的設備 機具都包含電力系統供其運轉,在電 力傳輸及使用過程中,必定經過交流 直流互轉 (A/D, D/A)、直流轉直流 (D/ D)、交流轉交流 (A/A) 等的數次功率轉 換,電力電子元件即應用在這些電力的 直交流變換上,及控制瞬間加壓的電流 穩定度等方面,圖一所示為不同的電力 電子元件操作時的功率及頻率與應用領域[1],而如何能更有效率地進行功率轉換,降低每次轉換過程中的功率耗損(power loss),達到節能的目的則成為電力電子元件的研究重點。由於國外廠商如 ST、Fairchild、Infineon、IR 等在此領域起步較早,對電力電子元件有深入研究且擁有可觀專利權,國內則是約近二十年左右才開始涉入此領域,起步落後許多,因此競爭上明顯居於弱勢,但以國內在半導體界的人才與能量而言,急起直追並不是完全沒有優勢。

圖一:電力電子元件應用領域及頻率[1]

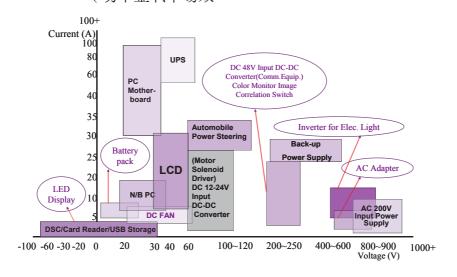

功率金氧半電晶體 (Power MOS-FET) 是最常被應用於功率轉換系統中 的電力電子元件,由於 MOSFET 的單 極性及電壓控制的特性,因此 Power MOSFET 具備了較高的輸入阻抗、較 低的驅動功率、較低的導涌電阳值、較 快的切換速度、較低的切換損耗及較大 的安全操作區。由於切換速度的優勢, 使得 Power MOSFET 滿足高切換速度 的應用,而 MOSFET 的電壓驅動的特 性讓控制電路在設計上較為簡單,加上 技術的成熟度,在多數的應用上配合成 本的考量因此使得 Power MOSFET 的 應用範圍越來越廣,在所有的分離式功 率元件中扮演著最重要的角色。圖二所 示為其在各個電壓與電流額度下的應用 示意圖。

# 二、Power MOSFET 的結構與 製作步驟

Power MOSFET (功率金氧半場效

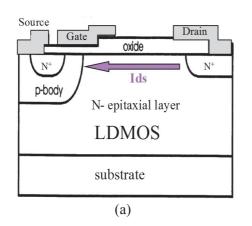

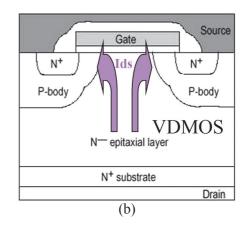

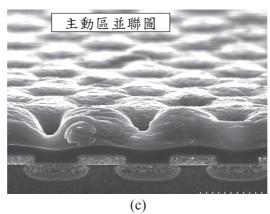

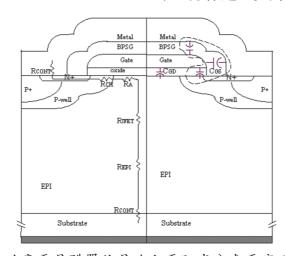

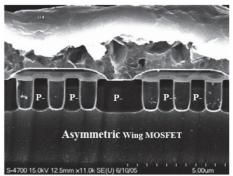

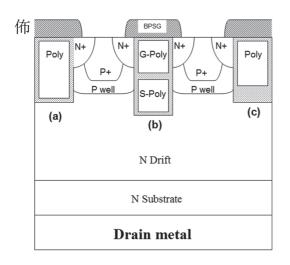

電晶體)在發展初期是以水平式結構 為主,其電流流向為水平結構,一般 稱 為 LDMOS(Lateral Double-Diffused MOS),如圖三(a)所示。水平式的結 構非常適合與目前積體電路整合使用成 為功率積體電路 (Power Integrated Circuit, Power IC), 但是因為其在大電流 需求下會浪費太多的晶片面積,故僅適 合使用高壓低電流電路。如果將其製作 成分離式 (Discrete) 元件應用在其他焊 接板子上,會浪費許多成本不符合經濟 效益,因此為了滿足大電流高功率的使 用,水平電流結構則轉為垂直型結構的 發展,如圖三(b)所示,一般稱作 VD-MOS (Vertical Double Diffused MOS) 或 是 DMOS,此處 D的定義為該元件的 通道是由兩次擴散後的長度所決定,而 與該元件的閘極長度無關。因為垂直式 結構使用晶片面積較水平式少很多,因 此取代水平式結構成為目前分離式元件 的主要結構。圖三(c)所示為各個圖三 (b) 單一元件晶胞 (cell) 並聯的 VDMOS

圖二: Power MOSFET 應用上所需之電壓與電流

圖三:(a)水平式功率金氧半場效電晶體,(b)垂直式功率金氧半場效電晶體(b)垂直式功率金氧半場效電晶體主動區 SEM 並聯圖

之 SEM 圖形,大電流或低電阻元件即取決於其並聯數目(元件主動區面積)。

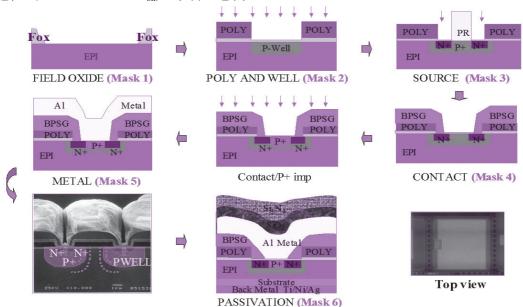

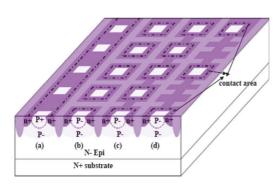

圖四所示為分離式垂直型 Power MOSFET 的簡化製程示意圖,此處我們以N型通道元件使用六張光罩為例,其光罩分別是主動區 (active region)、閘極 (gate)、源極 (source)、接觸 (contact)、金屬層 (metal) 及鈍化層 (passivation)。首先,對不同耐壓的元件先在基板 (substrate) 上成長所需耐壓厚度的 N型 磊晶層 (EPI),之後氧化成長場氧化層 (Field Oxidation),蝕刻該層定義出主動區及浮接場環 (floating field ring) 的位

置,之後再氧化成長閘極氧化層 (gate oxidation) 並沉積複晶矽 (poly-silicon),使用閘極光罩依序蝕刻複晶矽及閘極氧化層定義閘極及井區 (well) 後摻雜硼離子並加熱做離子趨入 (Drive-in) 及活化,接著使用源極光罩 (Source Mask) 定義並製作源極區域,接續沉積硼磷矽玻璃 (BPSG),使用接觸區光罩 (Contact Mask) 並蝕刻 BPSG 定義出源極接觸區,接著續作重摻雜 P型元素形成重摻雜區,以提升元件耐雪崩崩潰能量的能力,最後沉積金屬定義閘源極金屬後,再沉積氮化矽 (Si<sub>3</sub>N<sub>4</sub>) 做為鈍化層保護,

並以鈍化層光罩定義鈍化層範圍,最後 研磨基板後再做背金處理,至此元件結 構大致完成。

## 三、Power MOSFET 的幾個重要 特性

Power MOSFET 為一種單載子導電的單極型電壓控制元件,它具有開關速度快、輸入阻抗高、驅動功率小、熱穩定性優良、高頻特性好、安全工作區 (SOA) 寬、工作線性度高,且較無雙載子導電元件之二次擊穿問題 (Second Breakdown)。在各類功率電路開關中應用極為廣泛,並且市場商機龐大,全世界有數百億美元的市場。其所扮演的角色為一個切換元件,其所要求的規格包含崩潰電壓值 (Breakdown voltage)、導通電流 (On-current)、導通電阻 (On-resistance; R<sub>on</sub>)、閘極電荷

(Gate charge; Q。)、啟閘值電壓 (Threshold voltage;V,)、雪崩崩潰電流/能量 (Avalanche current/energy; Ias/Eas ) 輸入 電容 (Input capacitance; Ciss )、輸出電 容 (Output capacitance; Coss )、逆向轉換 電容 (Reverse Transfer capacitance; Crss ) 與延遲時間 (Delay time) 等,而在這些 參數中,其中又以崩潰電壓、導通電 流、導通電阻、閘極電荷及雪崩崩潰 電流/能量為各研究單位研究的重點, 因此如何設計出一顆擁有較高的耐壓、 較大的電流、較小的電阻及較低的閘極 電荷的元件,並在其中取得平衡,一直 是研究的重要課題。尤其各家在設計此 元件時通常皆以導通電阻值 (R.,,)× 閘 汲極電荷 (Gate charge; Qod) 的大小為評 量指標 (figure of merit)[2-3], 此值暗指 的涵義為元件功率消耗多寡,該值與面 積無關,導通電阻值決定了元件導通 時的損耗功率 (conduction loss),而閘

圖四:垂直型功率金氧半場效電晶體簡化製程示意圖

汲極電荷決定了元件切換時的損耗功率 (switching loss)。

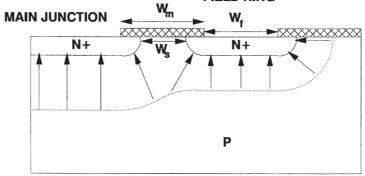

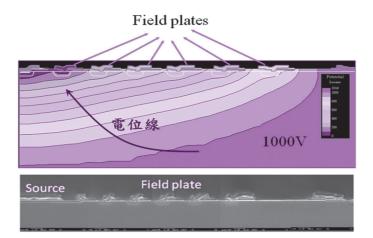

Power MOSFET 的在設計或使用 上有幾個特性需要特別注意。其額定 耐壓 (breakdown voltage) 與導通電阻值 (on-resistance) 是其兩個最重要的基本 特性,決定了該元件可否使用於某電 路上的基本門檻。由於 Power MOSFET 作為一個用在電源控制轉換的核心元 件,元件必須滿足電路上的耐壓與通過 的電流,此系統電流對於元件而言在考 慮功率消耗的前提下即元件在導通時的 等效電阻值。由於 Power MOSFET 元 件的面積分為主動區和終端區兩塊,對 於耐壓而言,主動區是一個單純的 PN 崩潰電壓,耐壓的重點在於磊晶片的選 擇,困難的在於終端區的設計方是。 終端區有非常多種的設計方式,各有 其好處與專利,最常見的是利用保護 環 (guard ring 或另稱浮接場環,floating field ring) 和場板 (field plate) 的搭配來 延伸終端區的空乏區藉以降低該區表面 電場迫使元件崩潰點發生在主動區的設 計,如圖五所示為浮接場環延伸終端區 的空乏區的示意圖 [4]。基本上只要保 護環設計得宜夠好,理論上元件可以達 到任何想要的崩潰電壓值。圖六所示為 1000V 元件的終端區示意圖,其最左端

#### FLOATING FIELD RING

圖五:浮接場環延伸終端區的空乏區的示意圖 [4]

圖六:1000V 元件的終端區示意圖

為元件的主動區亦為元件的源極端,底 部及最右部為汲極區。適當的保護環和 場板的設計可以降低元件的終端區電 場,使得元件崩潰電壓完全由磊晶片和 主動區的設計決定

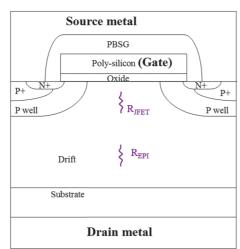

Power MOSFET 的 另一個 重要特性即為元件之導通電阻值 (on-resistance),對使用電路者而言即是導通電流,對元件設計者或製造商而言設計的方式是控制元件導通狀態的等效導通電阻值,分離式元件最終會有其封裝形式,不同的封裝有其最大可容許的散熱功率,此散熱功率經由元件之導通電阻值決定了元件的導通電流。圖七所示為一般平面式 (planar) 功率電晶體之單位晶胞 (Unit cell) 剖面示意圖,其中左半部為各導通電阻的組成及分佈,平面式功率金氧半場效應電晶體之導通電阻值R<sub>on</sub>之式子如下所示

$$\begin{split} R_{\text{on}} = & R_{\text{CONT\_D}} + R_{\text{sub}} + R_{\text{EPI}} + R_{\text{JFET}} + R_{\text{CH}} + R_{\text{CONT\_S}} \\ & \text{Equ (1)} \end{split}$$

R<sub>CONT\_D</sub> 為汲極 (Drain) 與基座的接面電阻,R<sub>sub</sub> 為基座電阻,R<sub>EPI</sub> 為磊晶層電阻,R<sub>IFET</sub> 為接面場效應電阻,R<sub>CH</sub> 為通道電阻,R<sub>CONT\_S</sub> 源極 (Source) 接面電阻。由於元件金屬接觸端與晶片基座均為高摻雜濃度,故 Equ(1) 可化減為

$$R_{on} = R_{EPI} + R_{JFET} + R_{CH}$$

Equ (2)

在中高壓元件中,為了達到高耐壓的設計,元件磊晶層通常摻雜較淡且較厚,故 Equ(2) 可再化減為

$$R_{on} = R_{EPI} + R_{J} \sim R_{EPI}$$

Equ (3)

我們可以發現隨著  $V_{BR}$  的增加,  $R_{IFET}$  及  $R_{EPI}$  所佔比重逐漸提高 [4]。

有非常多種的設計方式可以針對 Equ (2) 的阻值做改善的動作,低阻值 的設計對設計者是很重要的功課,直接 影響到元件特性及成本考量,我們將再 下一節作進一步討論。

圖七:功率電晶體單位晶胞之電阻成分與電容示意圖

圖八:(a) 閘極電荷量測電路,(b) 簡化量測圖形

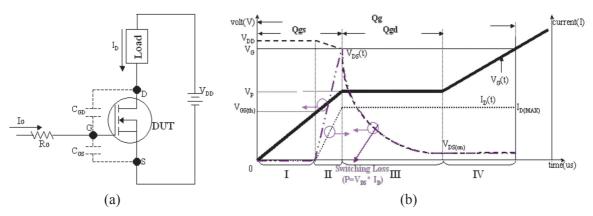

而圖七右半部所示為平面式功率 電晶體的輸入寄生電容示意圖,其大 小會影響到閘極的充放電電荷值,而 導致造成此元件在切換時的切換損失 (switching loss),一般量測是量測此元 件的閘極電荷大小。圖八 (a) 所示為一 般常見的量測電路[5],於測試元件輸 入端輸入一個電流 (I<sub>G</sub>),進而量測閘極 電壓對時間的關係, 閘極電荷的大小 即為(I<sub>G</sub>×time),圖九(b)所示為一般 常見的量測圖形,黑實線部分為閘極電 壓,虛線部份為汲極電壓,橫軸單位為 時間(或電荷),藍色部位為切換功率 消耗,我們可以看到當時間 B 到 D 段 的元件電流與電壓均不為零,因此此段 時間中會產生切換損失,如何降低這兩 段時間的閘極電荷,尤其是閘汲端電荷 這段時間便成為發展功率元件的重點。 一般而言愈大的閘汲極相疊而積,閘極 電荷越高,越不利元件操作在高速切換 的電路,尤其是元件中的間汲極電容值 大小更是影響此值的重要參數。降低閘 汲端電荷對於電力電路上的應用可以大 幅減少切換損失,降低元件操作時溫 度,達到節約能源的效果。

圖七中的右半部的各電容值亦影 響了此元件在操作頻率上的限制。Power MOSFET 中的 capacitor 依其視入的 端點不同,可分為輸入電容 Ciss (input capacitor)、輸出電容 Coss (output capacitor) 及逆向轉換電容 Crss (reverse transfer capacitor)。而此三種電容則是由三個 端點之間的電容所組成,分別是:Gate 及 Source 電容 C<sub>GS</sub>、Gate 及 Drain 電容 C<sub>GD</sub> 以及 Source 及 Drain 電容 C<sub>SD</sub> 所引 起,其中逆向轉換電容 Crss 也有人稱為 回授電容或米勒電容。而米勒電容在不 同的應用電路上將會與電路上的電阻形 成一個對元件輸入端的極點,此外電路 上的電阻與元件的米勒電容在元件的切 換操作上將導致另一種的耗能現象,因 此降低這些電容對於減少切換損失及提 昇元件操作頻率有很大的幫助。

此外元件在應用電路上使用時, 根據不同的負載條件會有不同的耐用性 問題,幾個較少被研究但在電力電路應

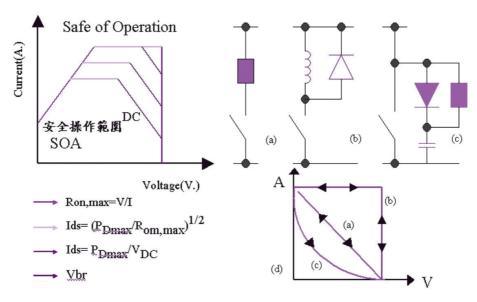

用上相當重要的特性一是應用在電感性 負載時,元件在切換時受到的反向逆電 動勢能量,元件對於宣洩此能量的能力 稱為元件的強健性,不考慮此特性的元 件在電感性負載的電力電路中將非常容 易被擊穿燒毀,尤其近年來對於眾多電 路的大電流要求,此一特性越顯重要, 一般設計是提升元件的耐雪崩崩潰電 流(或崩潰能量)。一般功率元件在應 用時多扮演著切換的角色,應用上就必 須考慮其環境對它的影響,我們會去 制定一個元件的安全操作範圍 (Safe of Operation Area; SOA),安全工作區是指 元件在不損壞情形下,所能操作的最大 極限,也就是說,是定義出元件在避免 二次崩潰 (Second Breakdown) 情形下, 所能同時操作的最大元件電壓及最大元 件電流的極限。SOA 是的極限是由最 大可接受的功率損耗 (Power Loss)、最 大可接受的電流及最大可接受的電壓所

限制,而不同的封裝形式會影響到元件的散熱能力而有不一樣的 SOA 圖形。而在電感性負載切換的情形下,由於元件必須承受電感所產生的電性應力,因此元件的 SOA 就顯得相當重要。

圖九所示為元件的安全操作範圍 (Safe of Operation Area; SOA),安全操 作範圍由四條曲線組成,分別是崩潰電壓 (藍線)、導通電阻值 (紅線)、額定電流 (綠線,由最大功率消耗限制)與功率線 (紫線,由最大功率消耗限制),圖中 (d) 分別為元件使用在電阻性 (a)、電感性 (b) 與電容性 (c) 負載時,元件與安全操作範圍之關聯圖,由圖中我們可以看到電感性負載時元件需要較強的抗外界能量變化承受度的設計,由於元件在電感性負載時會遭受到電感的反向逆電動勢,如無法把此能量宣洩掉,將導致元件的永久損壞.一般元件在電路 耐用的耐用性我們稱之為元件之強健

圖九:元件的安全操作範圍及負載電流電壓曲線圖

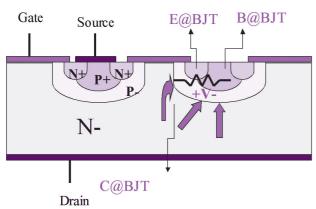

性 (ruggedness),圖十所示為元件在由導通至關閉的瞬間,能量會透過元件內部的寄生二極體宣洩掉 (avalanche 方式),但是元件內部還是有另一個寄生的 BJT,如在宣洩過程中,圖中 V 值大於 0.6V,BJT 便會啟動,而導致元件的燒毀,改善的方式可以加入圖中的P+的製程使的電流宣洩的過程 V 值不會大於 0.6V,製程步驟中的重摻雜 P型元素形成重摻雜區即為提升此一元件特性的製作方式,P+的範圍越寬越廣對元件的耐用性越好,有非常多種的方式或加上額外的光罩都可以對元件的雪崩電流/能量提出改善的動作 [6]。

## 四、未來技術發展趨勢

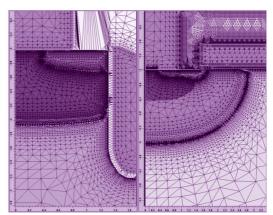

Power MOSFET 的發展趨勢是朝向低成本、高頻率、高耐壓低阻值高電流、低切換損失的方向發展,此外在於元件的強健性跟可靠度方面仍然需要小心考量。在高耐壓設計時需要小心設計控制元件內部的電場值大小不會到犧牲掉可靠度的狀態,發展搭配元件模擬軟

體的設計可以減少設計的時程及開發成本。尤其是高耐壓的設計與超低電阻及特殊結構的開發,市售的元件及製程軟體可以扮演非常有用的角色,可以完全匹配於半導體製造廠的製程參數來開發元件,如圖十一所示。

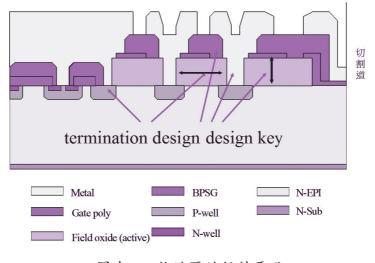

高壓功率元件從發展至今,其終 止區為達到一個額定的崩潰電壓,其 設計方式有斜面曲線場 (beveled contour), 有限場環 (Filed-limiting Ring) 或 稱保護環 (Guard Ring),終端接面延伸 (junction termination extension, JTE), 半絕緣多晶砂 - 砂接面 (semi-insulating poly-crystalline silicon, SIPOS,降低表面 電場 (reduced surface field, RESURF), 場板 (Field Plate), 平面變化擦雜 (Variation of lateral doping, VLD),淺溝 槽氧化填充 (Shallow trench filled with oxide) 等,各有其特殊的地方。而目前 高壓功率元件的終端區設計較主要以保 護環及場板,或兩者的混合體為主[7]。 近年亦有其他其他的方式如保護環配合 深溝渠的方式來大幅縮短元件終端區的 方式。不論是何種方式,都是要元件

圖十:元件崩潰時電流路徑圖

圖十一: 元件模擬結構剖面圖

終端區的電場要有一個合理的下降及延 伸來達到高耐壓的設計,如圖六所示。 終端區的設計不像元件主動區左右前後 各有其他的單位晶胞 (unit cell) 空乏區 的保護,如何的設計出一個額定的崩潰 電壓是一回事,如何讓此崩潰電壓可以 長時間的操作又是另一種設計的考量, 不良的元件終端區設計使的元件製作完 雖然可以量測到額定耐壓,但由於高功 率(高電壓、高電流)的使用,很容易 導致元件漸漸的失效,最常見的可靠度 測試結果不是元件直接燒毀就是耐壓隨 時間衰減。因此空乏區的設計諸如製程 條件及各井區之間的距離及場板的高度 與相對位置等不只影響到其可承受的耐 壓,也影響其耐用程度的可靠度圖十二 所示為終止區的結構示意圖,會影響的 地方有非常多,如圖中 design key 所示, 如何系統的分析各個因素間對耐壓的相 關性,透過元件內部電場的分析來得到 一個可靠穩定的高耐壓元件是設計的重 點,而不是僅僅設計出一個預定額定崩

潰電壓元件,而不管其是否真正可適用 的高壓功率元件,其設計重點在於保證 終端區的崩潰值大於元件內部主動區的 崩潰值。

另外在其他材料及元件結構上的 設計也是高壓 Power MOSFET 發展的 重點,透過材料及元件結構的設計來 達成低阻值及低閘極電荷設計以降低損 耗。受限於矽晶材料的特性而難以將 power MOSFET 特性大幅提升,寬能隙 (wide bandgap) 材料的使用成為另一個 發展方向,目前最被廣泛研究的寬能隙 材料為碳化矽(SiC)及砷化鎵(GaN), 其具有較矽晶材料更高的臨界電場及電 子遷移率如表一所示,其材料具備出較 矽晶元件能承受更高的電壓及更高的輸 出電流,因此被視為明日之星,但基板 尺寸及價格問題在無法完全克服下,即 便特性遠優於矽晶材料元件,仍難取代 矽晶材料元件,在應用上仍受限制,因 此 power MOSFET 發展方向仍舊以矽 晶材料元件為主,並持續透過結構上的

圖十二:終端區的設計要點

表一: 寬能隙材料特性比較

| Material | E <sub>g</sub> @300K<br>(eV) | μ <sub>n</sub><br>(cm²/Vs) | V <sub>sat</sub><br>(10 <sup>6</sup> cm/s) | E <sub>c</sub> (10 <sup>6</sup> V/cm) | εγ   |

|----------|------------------------------|----------------------------|--------------------------------------------|---------------------------------------|------|

| Si       | 1.12                         | 1450                       | 10                                         | 0.3                                   | 11.7 |

| 4H-SiC   | 3.2                          | 900                        | 22                                         | 3                                     | 10   |

| GaN      | 3.4                          | 2000                       | 25                                         | 3.5                                   | 8.9  |

改良來提昇元件特性。研究最多最廣的兩個元件結構即是 IGBT(Insulated Gate Bipolar Transistor) 和 Super Junction 元件。

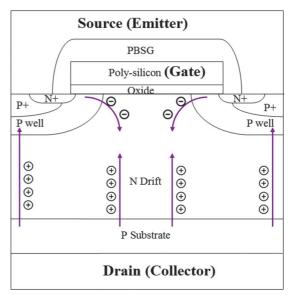

IGBT 結合傳統 VDMOS 的操作頻 率和控制電路設計的優點及 BJT 的高 輸出電流。IGBT 適用於頻率在 1k~10k 的範圍及較高功率的應用,而 VDMOS 則適合 10k 以上的高頻低功率的應用。 IGBT 與 VDMOS 主體結構大致相同, 最大的區別是基座的使用,如圖十三所 示,在正常操作下,汲極會接正電壓, P型基座(集極)與N型磊晶層的接面 會順向偏壓,因此,大量的電洞注入磊 晶層,使得磊晶層的電值降低,大幅 的減少從汲極至源極的串聯電阻,因此 有高輸出電流的表現。但由於電洞在磊 晶層中是屬於少數載子,關閉時需完全 被移除,否則會有關閉不完全的情形。 因此當閘極關閉時,電子不再從源極 (射極)注入,因此電洞的移除必須靠 再結合 (recombination) 的費時過程。所 以 IGBT 的操作頻率要比傳統 VDMOS 低,而改善此問題也是此元件的重要設 計課題。而閂鎖效應 (Latch-Up) 是設計 IGBT 時的缺點之一,latch-up 的能力 決定 IGBT 能夠導通的電流量,latch-up 的原因是由寄生 NPN(N+/P well/N drift) 與 PNP(P well/N drift/P substrate) 所 形成的 NPNP 結構,也就是寄生的閘流體 (thyristor) 導通造成,如果寄生 thyristor 導通,NPN 及 PNP 會組成一迴路而有一相當大電流在此迴路中且不受閘極的控制,元件可能因此而燒毀。要解決 latch-up 問題,則必須降低 PNP 或 NPN 的增益 (gain) 著手。

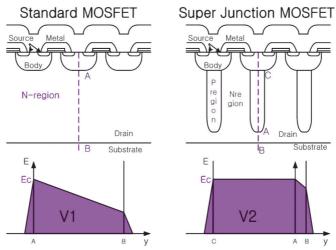

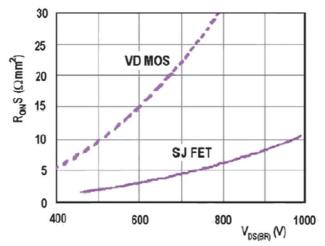

Super-junction 是近年最被看好的 power MOSFET,其低導通電阻的表現 在 400V 至 1000V 遠優於 VDMOS [1],

圖十三:IGBT 結構及導通電流示意圖

而結構上最大不同點是在原有的P型 井區下延伸一P型區域,此P型區域 濃度較P型井區略低,如圖十四所示 為元件示意圖及的內部電場分佈示意圖 [8],向下延伸的P型區域可以有效分 散電場,使的電場分布由垂直型變成水 平式,避免電場過度集中於井區底部, 亦拉高厚磊晶垂直區的電場,電場對距 離積分下在相同的磊晶片上會大幅增加 元件耐壓,因此對於設計者而言,製作 出相同的耐壓元件磊晶片可以減薄, 濃度可以提升,此結構改變了原 Power MOSFET 由 PN 結構耐壓設計的耐壓與空乏區的物理限制,因此大幅的降低了元件導通時的電阻值,如圖十五所示,由於元件阻值與耐壓物理曲線斜率是不同機制造成,故 super-junction 結構的導通電阻可以較 VDMOS 低。而 P型區域的濃度及磊晶層濃度的電荷平衡 (charge balance) 成為設計 super-junction的關鍵,如何精準控制濃度成為製程與設計上的考驗。

圖十四: VDMOS 與 super-junction 結構及垂直方向電場分布圖 [8]

圖十五: VDMOS 與 super-junction 電阻比較圖 [9]

16

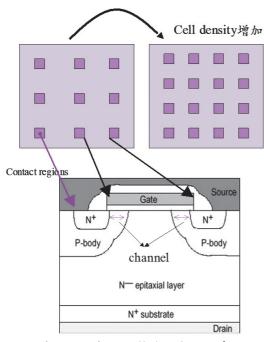

功率元件之特性比較在相同的耐 壓條件下一般是以此元件之導通電阻 值 (Ron)× 閘汲極電荷 (Gate charge; Qod) 的大小為評量指標 (figure of merit)。在 不同的面積下,面積越大的元件其並聯 的流通電流路徑越多,因此圖七左邊的 並聯電阻支路越多,元件可導通的電流 越大,其相對的等效電阻值越低,而阻 值大小與元件面積成反比,早期的研 究者以單位面積下越低的導通電阻值 (specific on resistance, Rsp(常見單位為 mΩ-mm²)) 判別來定義元件優劣,將元 件的單位晶胞長度 (cell pitch) 作小,可 以增加元件的晶胞密度 (cell density) 與 電流密度,如圖十六所示。圖十六中晶 胞密度的上升也造成閘極面積的增多進 而提高了閘極電荷的大小,而增加了元 件切換時的切換損耗。間汲極電荷的大

圖十六:增加 cell density 示意圖

小與元件面積是成正比,設計者在設計元件時被要求再下降導通電阻值時不能犧牲(提高)閘汲極電荷值,因此拿元件之導通電阻值  $(R_{on}) \times$ 閘汲極電荷 (Gate charge;  $Q_{gd}$ ) 的大小為元件優劣設計評量指標 (figure of merit, FOM)[2-4]已經是常見的公認判斷準則,其值與元件面積大小無關 (一個正比,一個反比於面積,相乘時面積因子會抵銷掉)。

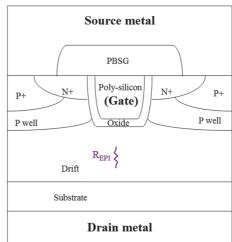

為了降低元件操作損耗,必須由 降低元件導通阻值及閘極電荷著手, 高壓 Power MOSFET 阻值由於 R<sub>EPI</sub> 及 R<sub>IEET</sub> 佔據相當大比例,而為了降低元件 的阻值,則必須針對 Rept 及 Riest 進行 改善。針對降低 R<sub>EPI</sub>,必須將磊晶層做 最佳化設計;而針對降低 R<sub>IEET</sub>,則可以 進行晶胞設計或利用雙層磊晶片或者額 外離子佈值於閘極下方 R<sub>IEET</sub> 用以減少 其影響。在低壓 Power MOSFET 上由 於阻值在RCH及RIFET佔據了大部分比 例,因此提升總閘極寬度與減少 R<sub>IEIT</sub> 的結構變成為設計的重點。目前流行的 是使用溝槽式閘極 (trench gate) 的方式, 所謂溝槽式閘極即是將閘極埋入矽晶中 如圖十七所示,此方式可減少甚至完 全消除相鄰井區所造成的寄生 JFET 效 應,可有效降低元件阻值。此外,由於 溝槽式閘極元件的誦道是垂直式結構, 與傳統結構水平式不同,可以對晶圓面 **積做更妥善的利用,隨著挖溝槽技術的** 改善, Power MOSFET 的單位晶胞間極 可以從數微米減少至 0.2 微米,再配合 一些製程技術圖十六的源極 N+ 甚至不 需要光罩定義, cell pitch 可以從早期的

圖十七溝槽式閘極功率金氧半電晶體

圖十八:溝槽式閘極功率金氧半電晶體,(a) 開放式晶胞設計,(b) 封閉式晶胞設計, (c) 羽翼狀晶胞設計,(d) 非對稱式羽翼狀晶胞設計

10 幾微米迅速改善到一微米左右,大幅提高單位面積的晶包密度與改善元件的總通道寬度,進一步的提升通道寬度則可以利用自我對準的概念或羽翼狀晶胞的設計 [10],如圖十八所示。結合晶圓面積率的提升與 R<sub>JFET</sub> 的消失,低壓 Power MOSFET 的阻值可以非常大幅被降低。另一個伴隨的好處是晶胞閘極的巨幅縮小,使得閘汲極重疊面積變小,也迅速的改善了 Q<sub>od</sub> 的數值。

為了改善元件切換損耗,必須降低元件閘極電荷著手,由於電荷與電容成正比,降低電荷就必須減少電容,而電容與面積成正比而與厚度成反比,因此,可以藉由減少閘極面積或增加氧化層厚度來改善,特別是與元件切換速度直接相關的閘汲極面積。為了減少閘汲極面積,使用全面性離子佈植方式配合短閘極結構或分離式閘極結構來達成,全面性離子佈植是在定義閘極前做表面

圖十九:(a) 一般溝槽式閘極,(b) 分離 閘極,(c) 加厚底閘極氧化層

植,目的是為了提高磊晶層表面濃度來縮短閘極長度而不影響元件阻值,而分離式閘極則是將部分的閘汲極氧化層移除;亦或是部分增加閘極中心氧化層厚度。在溝槽式閘極功率金氧半電晶體的設計上亦有做底閘汲極氧化層加厚或是分離閘極(split gate)的方式屏障閘汲極面積來改善閘汲極電荷,如圖十九所示。

#### 五、結論

面對能源日益枯竭的今日,除開發替代能源外,節能更是重要課題,有效率地進行功率轉換,降低每次轉換過程中的耗損達到節能的目的。雖然目前power MOSFET 市場仍以 VDMOS 為大宗,但隨著半導體製程的快速精進,同時帶動電力電子技術上的突破與成長,各類製程及結構上的研究及技術上的日

新月異的發展將帶動另一波功率元件的提升,對於能源轉換效率的上有相當大幫助。本文對 power MOSFET 的設計及重要電性與未來發展做簡短說明,期望能對剛進入此領域者於進行設計與研究時有些許幫助。

## 參考文獻

- [1] S. Linder, Potentials, Limitations, and Trends in High Voltage Silcon Power Semiconductor Devices, Proc. ISPSD'08, PP.11-20, 2008.

- [2] A. Q. Huang, "New Unipolar Switching Power Device Figures of Merit" IEEE Electron Devices Lett., vol. 25, pp. 298-301, 2004.

- [3] F. T. Chien, C. N. Liao, C. L. Wang, and H. C. Chiu "High Performance Power MOSFETs by Wing-cell Structure Design", the Institute of Electronics, Information and Communication Engineers, IEICE, VOL.E89-C, No.5, pp. 591-595, 2006.

- [4] B. J. Baliga, "Power Semiconductor Devices," Massachusetts: PWS, 1996.

- [5] A. J. Yiin, R. D. Schrimpf, and K.F. Galloway, "Gate-Charge Measurements for Irradiated N-Channel DMOS Power Transistors", IEEE Trans. Nucl. Sci., vol. 38, pp. 1352-1358, 1991.

- [6] K. J. Fischer, K. Shenai, "Dynamics of Power MOSFET Switching Under Unclamped Inductive Loading Conditions," IEEE Trans. Electron Devices, vol. 43, no. 6, pp. 1007-1015, 1996.

- [7] C. B. Goud and K. N. Bhat, "Two-dimensional analysis and design considerations of high-voltage planar junctions equipped with field plate and guard ring", IEEE Trans. Electron Devices, VOL.38, pp.1497-1504, 1999.

- [8] C. K. KIM, J. M. GEUM, and Y. T. KIM, "Effects of Charge Imbalance on Super Junction Power MOSFET", Recent Advances in Telecommunications and Circuits, pp.27-30.

- [9] V. Benda, "Power Semiconductors State of the Art and Future Trends", Global Journal of Technology and Optimization, Vol. 2, pp.29-36, 2011.

- [10] F. T. Chien, C. N. Liao, C. L. Wang, H. C. Chiu, and Y. T. Tsai, "Low On-Reesistance Trench Power MOSFETs Design", Electron. Lett., vol. 44, no.3, pp. 232-234, 2008.

#### 作者簡介

簡鳳佐

經歷:逢甲大學電子系教授